Verilog HDL: VLSI Hardware Design Comprehensive Masterclass

- Descrição

- Currículo

- FAQ

- Revisões

A job oriented exhaustive course on logic design for hardware using the Verilog Hardware Description Language.

Unique, tested and proven structured style and approach followed.

Thoughtful blend of theory and practice for your learning.

Unlimited support with the instructor.

Understand all the intricate details in thinking and understanding hardware design.

Principles are reinforced with multiple examples.

Good coding guidelines and bad examples to avoid.

After completing the course, you can confidently write synthesizable code for complex hardware design.

Thorough discussion of every hardware component design.

Detailed explanation of the relationship between code and digital hardware units.

Freely download 100+ code examples and test benches used in the course.

Access to all the materials and the future upgrades.

Loads to quizzes and assignments to check your understanding.

Work through the lessons at your own pace.

-

1IntroductionVídeo Aula

Get the basics right to lay a strong foundation

-

2Course coverageVídeo Aula

-

3Review of VLSI conceptsVídeo Aula

-

4Quick CMOS basics (added as per request)Vídeo Aula

-

5What is VLSI?Vídeo Aula

-

6Review of termsVídeo Aula

-

7Minimum feature sizeVídeo Aula

-

8Why Integration?Vídeo Aula

-

9Broad areas in VLSIVídeo Aula

-

10VLSI Design Styles - Full CustomVídeo Aula

-

11VLSI Design Styles - Semi CustomVídeo Aula

-

12VLSI Design Styles - FPGAVídeo Aula

-

13VLSI Design Styles - Gate ArrayVídeo Aula

-

14VLSI Design Styles - ComparisonVídeo Aula

-

15Full custom vs Semi customVídeo Aula

-

16ASIC vs FPGAVídeo Aula

-

17ASIC Design Flow - Part 1Vídeo Aula

-

18ASIC Design Flow - Part 2Vídeo Aula

-

19ASIC Design Flow - Design SpecsVídeo Aula

-

20ASIC Design Flow - ArchitecturingVídeo Aula

-

21ASIC Design Flow - RTL codingVídeo Aula

-

22ASIC Design Flow - VerificationVídeo Aula

-

23ASIC Design Flow - SynthesisVídeo Aula

-

24ASIC Design Flow - Design for TestabilityVídeo Aula

-

25ASIC Design Flow - Timing AnalysisVídeo Aula

-

26ASIC Design Flow - Floorplanning, Placement & RoutingVídeo Aula

-

27ASIC Design Flow - Formal VerificationVídeo Aula

-

28ASIC Design Flow - Power EstimationVídeo Aula

-

29ASIC Design Flow - FabricationVídeo Aula

-

30ASIC Design Flow - PackagingVídeo Aula

-

31Verilog Design StylesVídeo Aula

-

32My First Dataflow Style DesignVídeo Aula

-

33My First Behavioral Style DesignVídeo Aula

-

34My First Structural Style DesignVídeo Aula

-

351-bit Full Adder (Sturctural-1)Vídeo Aula

-

361-bit Full Adder (Sturctural-2)Vídeo Aula

-

371-bit Full Adder (Sturctural-3)Vídeo Aula

-

381-bit Full Adder (Dataflow)Vídeo Aula

-

391-bit Full Adder (Behavioral)Vídeo Aula

-

40My first Test BenchVídeo Aula

-

414 Valued LogicVídeo Aula

-

42Data TypesVídeo Aula

-

43Number RepresentationVídeo Aula

-

44Bit and BusVídeo Aula

-

45Naming ConventionsVídeo Aula

-

46Operators - BitwiseVídeo Aula

-

47Operators - ArithmeticVídeo Aula

-

48Operators - LogicalVídeo Aula

-

49Operators - RelationalVídeo Aula

-

50Operators - ReductionVídeo Aula

-

51Operators - ShiftVídeo Aula

-

52Operators - ConcatenationVídeo Aula

-

53Operators - RepetitionVídeo Aula

-

54Operators - ConditionalVídeo Aula

-

55Output Resolution TableVídeo Aula

-

564-bit Full Adder (Structural)Vídeo Aula

-

574-bit Full Adder (Dataflow)Vídeo Aula

-

584-bit Full Adder (Behavioral)Vídeo Aula

-

594-bit Full Adder Test BenchVídeo Aula

-

602:1 Multiplexer (Dataflow)Vídeo Aula

-

612:1 Multiplexer (Behavioral)Vídeo Aula

-

624:1 Multiplexer (Dataflow1)Vídeo Aula

-

634:1 Multiplexer (Dataflow2)Vídeo Aula

-

644:1 Multiplexer (Dataflow3)Vídeo Aula

-

654:1 Multiplexer (Behavioral)Vídeo Aula

-

662 X 4 Decoder (Dataflow)Vídeo Aula

-

672 X 4 Decoder (Behavioral)Vídeo Aula

-

683 X 8 Decoder (Dataflow)Vídeo Aula

-

694 X 2 Encoder (Dataflow)Vídeo Aula

-

704 X 2 Encoder (Behavioral)Vídeo Aula

-

714 X 2 Priority Encoder (Behavioral)Vídeo Aula

-

724 X 2 Priority Encoder (Dataflow)Vídeo Aula

-

734-bit Comparator (Dataflow 1)Vídeo Aula

-

744-bit Comparator (Dataflow 2)Vídeo Aula

-

754-bit Comparator (Behavioral)Vídeo Aula

-

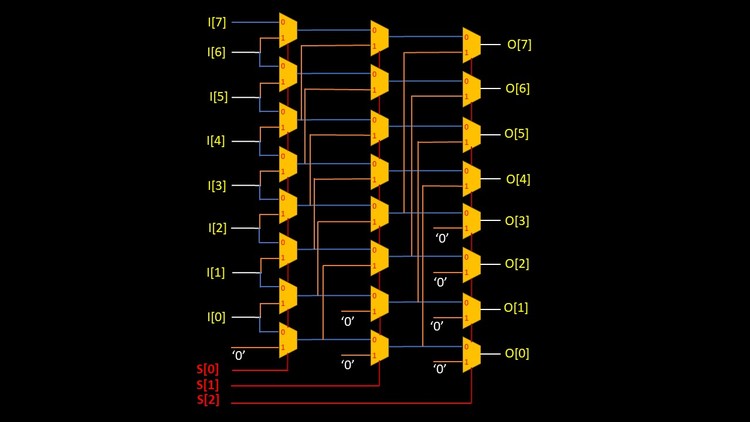

768-bit Barrel Shifter (Combinational Left & Right)Vídeo Aula

-

77Designing Arithmetic & Logic Unit (ALU)Vídeo Aula